# ARICH

# Multibit Data Storage States Formed in Plasma-Treated MoS<sub>2</sub> Transistors

Mikai Chen, Hongsuk Nam, Sungjin Wi, Greg Priessnitz, Ivan Manuel Gunawan, and Xiaogan Liang\*

Department of Mechanical Engineering, University of Michigan, 2011 W.E. Lay Automotive Laboratory, 1231 Beal Avenue, Ann Arbor, Michigan 48109, United States

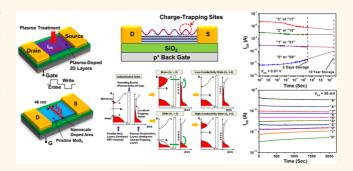

**ABSTRACT** New multibit memory devices are desirable for improving data storage density and computing speed. Here, we report that multilayer MoS<sub>2</sub> transistors, when treated with plasmas, can dramatically serve as low-cost, nonvolatile, highly durable memories with binary and multibit data storage capability. We have demonstrated binary and 2-bit/transistor (or 4-level) data states suitable for year-scale data storage applications as well as 3-bit/transistor (or 8-level) data states for day-scale data storage. This multibit memory capability is hypothesized to be attributed to

plasma-induced doping and ripple of the top MoS<sub>2</sub> layers in a transistor, which could form an ambipolar charge-trapping layer interfacing the underlying MoS<sub>2</sub> channel. This structure could enable the nonvolatile retention of charged carriers as well as the reversible modulation of polarity and amount of the trapped charge, ultimately resulting in multilevel data states in memory transistors. Our Kelvin force microscopy results strongly support this hypothesis. In addition, our research suggests that the programming speed of such memories can be improved by using nanoscale-area plasma treatment. We anticipate that this work would provide important scientific insights for leveraging the unique structural property of atomically layered two-dimensional materials in nanoelectronic applications.

KEYWORDS: 2D layers · MoS<sub>2</sub> · transistor · memory · plasma etching · charge trapping

Ithough solid-state drives (SSDs) based on flash memory technology are extremely popular nowadays, they are still about 7 to 8 times more expensive per unit of storage than hard disk drives (HDDs). To produce much cheaper SSDs, it is desirable to develop new low-cost memory fabrication processes as well as new memory architectures for improving the storage density. One of such efforts is to create multibit data storage memory devices to achieve a higher storage density.<sup>1-6</sup> The fabrication of multibit (or multilevel cell (MLC)) flash memories needs precise deposition of multiple semiconductor layers and multiple overlay lithography processes to create complicated memory transistors consisting of multiple floating gates and blocking and tunneling layers.<sup>1,2,7</sup> This significantly increases the complexity of memory cells.<sup>1,2,7</sup> Although the state-of-the-art production lines for MLC flash memories are mature enough to enable low-cost manufacturing of such complicated cells, the future scale-down of MLC circuits beyond Moore's law will lead to the need for new MLC prototypes with much

simpler architectures as well as new manufacturing systems with much lower processing cost and higher throughput. The recent efforts have demonstrated other prototype multibit memories based on different materials and device structures, including memories based on organic semiconductors with ambipolar transport properties,<sup>3,8</sup> memory transistors based on nanostructured materials,<sup>4</sup> flash memory-like transistors with capacitively coupled nanoparticle (NP)-based floating gates,<sup>5</sup> and multilevel resistive memories based on phase-change materials.9 Relatively complicated and expensive processes are still demanded for making these devices. Therefore, it is always desirable to develop new multibit memories with a unique combination of excellent retention and endurance property, simple structure, and low fabrication cost.

Two-dimensional (2D) semiconducting layered transition metal dichalcogenides (LTMDs, *e.g.*,  $MoS_2$ ,  $WSe_2$ , and  $WS_2$ ) are envisioned as attractive materials for making new field-effect transistors (FETs) with a unique combination of excellent electronic

\* Address correspondence to xiaoganl@umich.edu.

Received for review February 28, 2014 and accepted March 28, 2014.

Published online March 28, 2014 10.1021/nn501181t

© 2014 American Chemical Society

VOL.8 • NO.4 • 4023-4032 • 2014

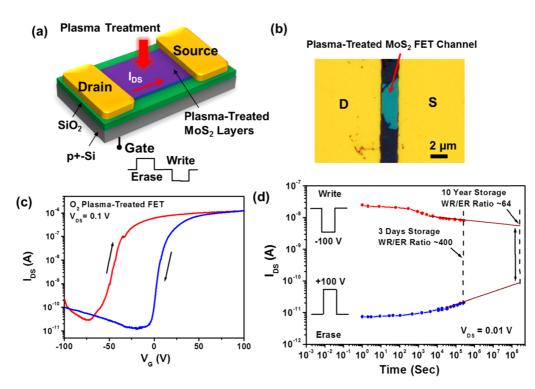

Figure 1. (a) Illustration of a back-gated MoS<sub>2</sub> memory FET created by a simple plasma treatment. (b) Optical micrograph of a memory FET consisting of an O<sub>2</sub> plasma-treated MoS<sub>2</sub> channel (thickness: 20 nm, length: 2  $\mu$ m, average width:  $\sim 5 \mu$ m), Ti/Au D/S contacts, and a p<sup>+</sup>-Si back gate. (c) Transfer curves ( $l_{DS}-V_G$  curves acquired along two different  $V_G$  sweep directions with a sweep rate of 10 V/s) and (d) retention characteristics ( $l_{DS}-t$  curves under  $V_{DS} = 0.01$  V and  $V_G = 0$  V recorded for 3 days) of the memory FET shown in (b). The insets in (d) show the  $\pm 100$  V, 1 s  $V_G$  pulses applied at the back gate for retention measurements. The WR/ER ratio after 3 days is measured to be ~400. The WR/ER ratio after 10 years is estimated to be ~64, which is suitable for long-term binary data storage.

and mechanical properties, low manufacturing cost, and potential large-area integration capability.<sup>10–24</sup> Especially, the stacking of MoS<sub>2</sub> layers and other 2D layers has been used for making new highperformance nonvolatile memory transistors.<sup>25–29</sup> These works have motivated and inspired additional research efforts to leverage unique electronic and structural properties of emerging 2D materials for making new material- and cost-efficient memory devices.

In this article, we present the fabrication and characterization of new MoS<sub>2</sub>-based floating-gate-free, nonvolatile, multibit memory FETs with excellent retention and endurance properties as well as extremely simple structures. These multibit memory FETs were dramatically created by treating MoS<sub>2</sub> FET channels with highly energetic plasmas. Using such plasmatreated MoS<sub>2</sub> FETs, we have demonstrated highly reliable binary and 2-bit (i.e., 4-level) data states with potential for year-scale data retention, as well as 3-bit (i.e., 8-level) data states suitable for at least day-scale storage. In addition, our research shows that the memory FETs fabricated by nanoscale-area plasma treatment exhibit a faster programming speed than the FETs made by blank plasma treatment. Such a new memory capability is hypothesized to be caused by the spontaneous separation of plasma-doped MoS<sub>2</sub> layers from undoped layers, which could form an ambipolar

charge-trapping layer interfacing the FET channel through a tunneling barrier. This structure could enable the nonvolatile retention of charged carriers as well as the reversible modulation of polarity and amount of the trapped charge, therefore resulting in multilevel data states in FETs. Our Kelvin force microscopy results strongly support this hypothesis. This work may leverage the unique structural property of 2D materials for applications in the fields related to data storage technologies. The presented fabrication methods and device structures hold a significant potential to be further developed into a low-cost, upscalable memory solution for making future highperformance disposable electronic products such as electronic labels, digital newspapers, medical care tags, and point-of-care biosensors. In addition, the presented multibit memory solution based on simple plasma doping processes could fulfill the predictable needs associated with the future scale-down of MLC circuits very well because of its unique simplicity and compatibility with already established manufacturing facilities.

# **RESULTS AND DISCUSSION**

Figure 1a illustrates the conversion of a  $MoS_2$ -based back-gated FET into a memory FET through treating the top surface of the  $MoS_2$  channel with energetic plasmas (*i.e.*, CHF<sub>3</sub>-, CF<sub>4</sub>-, and O<sub>2</sub>-based plasmas

VOL. 8 • NO. 4 • 4023-4032 • 2014

generated in a reactive ion etcher (RIE)). The details about the initial FET fabrication and the plasma treatment are described in the Methods and Materials section. Figure 1b shows the optical micrograph (OM) of an exemplary MoS<sub>2</sub> memory FET treated with O<sub>2</sub> plasma (channel length:  $L = 2 \mu m$ ; channel width:  $W \approx$  $5 \mu m$ ; MoS<sub>2</sub> thickness:  $t_{MoS2} \approx 20 \text{ nm}$ ). The fabricated memory FETs are characterized following the measurement processes described in the Methods and Materials section.

First, we measured the transfer characteristics (i.e., drain-source current  $(I_{DS})$ -gate voltage  $(V_G)$  curves acquired along two different  $V_{\rm G}$  sweep directions with a sweep rate of 10 V/s under a fixed drain-source voltage  $(V_{DS})$ ) of an untreated pristine MoS<sub>2</sub> FET that exhibits a mild hysteresis, as shown in Figure S1 (see the Supporting Information). This mild hysteresis was attributed to the charging and discharging processes associated with the charge-trapping sites at the MoS<sub>2</sub>/ SiO<sub>2</sub> interface.<sup>30</sup> As indicated by the previous work, such charge-trapping sites can retain the trapped charge for relatively short time durations (trapping time constants ( $\tau$ ) range from 30 to 500 s),<sup>30</sup> not suitable for data storage applications. We subsequently measured the transfer characteristics of a MoS<sub>2</sub> FET treated with water vapor by using an atomic layer deposition (ALD) tool (see the Supporting Information for details of this treatment process). As shown in Figure S2a, this moisture-treated FET exhibits a much more prominent  $I_{DS} - V_G$  hysteresis as compared to the untreated FET. Such a large hysteresis was attributed to the high density of moisture-induced charge traps, and it motivated us to characterize the retention properties (*i.e.*,  $I_{DS}-t$  characteristics acquired under fixed  $V_{DS}$ and  $V_{G}$  after the initial settings of the FET with specific  $V_{\rm G}$  pulses) of the trapped charge (or potential binary memory states) in this moisture-treated FET. Figure S2b shows I<sub>DS</sub>-t curves of potential "write (WR)" and "erase (ER)" data states of this moisture-treated FET, which were configured by the application of  $\pm 100$  V, 1 s V<sub>G</sub> pulses. After the initial device settings, the I<sub>DS</sub> values of so-called "write" and "erase" states guickly relaxed to almost the same value after  $\sim$  1000 s. This test indicates that although the water molecules adsorbed on MoS<sub>2</sub> FETs can induce a prominent hysteresis of transfer curves, the charge-trapping times of such FETs are too short to enable long-term data storage.

In contrast to untreated and moisture-treated MoS<sub>2</sub> FETs, all plasma-treated FETs exhibit well-differentiated binary data states with excellent retention properties. For example, Figure 1c and d display transfer and retention characteristics of an O<sub>2</sub> plasma-treated FET (*i.e.*, the one shown in Figure 1b), respectively. This memory FET exhibits a high WR/ER ratio (*i.e.*,  $I_{\text{DS(WR)}}/I_{\text{DS(ER)}}$ ) that was measured to be ~10<sup>3</sup> after a 1 h retention test and ~400 after a 3-day retention test. Based on the 3-day retention test data plotted in

Figure 1d, the WR/ER ratio after 10 years is estimated to be  $\sim$ 64, which can still enable an unambiguous reading of distinguishable IDS values for "write" and "erase" states. Figure S3 in the Supporting Information shows the transfer and retention characteristics of exemplary CF<sub>4</sub> and CHF<sub>3</sub> plasma-treated MoS<sub>2</sub> memory FETs. CF<sub>4</sub> and CHF<sub>3</sub> plasma-treated FETs typically exhibit relatively lower WR/ER ratios (10 to 100 after 2000 s retention tests) in comparison with those of O<sub>2</sub> plasma-treated ones (100 to 1500 after 2000 s retention tests). These characterizations show that plasma-induced (especially, O2 plasma-induced) chargetrapping levels in MoS<sub>2</sub>, in comparison with the traps at MoS<sub>2</sub>/SiO<sub>2</sub> interfaces and moisture-induced traps, can retain trapped charges for a much longer time and are potentially suitable for long-term data storage applications. In addition, the areal density of such plasmainduced charge-trapping states can be estimated by using  $\sigma_{\rm N} = C_{\rm ox} \Delta V_{\rm G}/2e$ , where  $\Delta V_{\rm G}$  is the hysteresis window,  $C_{ox}$  is the gate dielectric capacitance, and e is the elementary charge.<sup>26</sup> As shown in Figure 1c,  $\Delta V_{\rm G}$  is about 50 V and  $\sigma_{\rm N}$  is estimated to be  $\sim 10^{12}$  cm<sup>-2</sup>.

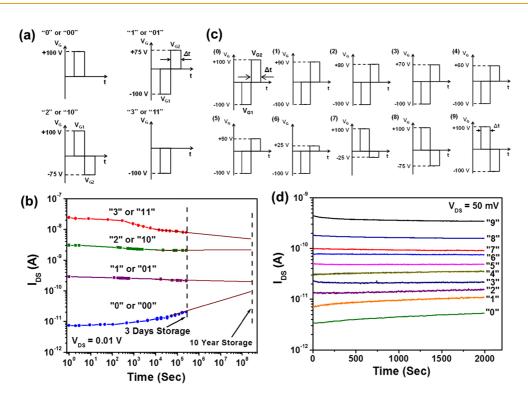

O<sub>2</sub> plasma-treated FETs were further used for demonstrating multibit storage capability. To obtain an n-bit/FET storage capability, a memory FET needs to have at least 2<sup>n</sup> distinguishable data levels. For example, the same FET shown in Figure 1d was used for realizing 2-bit storage that needs 4 data levels. Figure 2a sketches four V<sub>G</sub> signals used for configuring this memory FET into 4 data states ("00", "01", "10", "11"). Here, the signals labeled with "00" and "11" are exactly the same  $\pm$  100 V, 1 s V<sub>G</sub> pulse signals used for setting the FET into binary "erase" (now as "00") and "write" (now as "11") states, respectively. The  $V_{\rm G}$  signal for setting the "01" ("10") state is a dual-pulse signal that consists of one -100 V (+100 V), 1s pulse ( $V_{G1}$ ) immediately followed by another +75 V (-75 V), 1 s pulse  $(V_{G2})$ . Here, the first pulse  $(V_{G1})$  is used to release any previously trapped charge that has the same polarity as that of the to-be-refreshed charge or reset the FET back to the initial neutral state. The second pulse  $(V_{G2})$  sets the FET with a new charging state. Figure 2b shows the 3-day retention test data of 4 data levels. On the basis of the extrapolated  $I_{DS}-t$  curves (solid lines in log scales) shown in Figure 2b, these 4 data states are anticipated to be still distinguishable after 10 years. Therefore, this O2 plasma-treated MoS2 FET can serve as a 2-bit memory with a year-scale data storage capability.

Another  $O_2$  plasma-treated FET was set into 10 distinguishable data states ("0" to "9") by using the dual-pulse  $V_G$  signals sketched in Figure 2c. The second pulses ( $V_{G2}$ ) of these signals have different polarities and amplitudes, which can result in different amounts and polarities of the trapped charge in the FET and therefore generate multiple data levels. Figure 2d shows the retention behaviors of these 10 data levels. On the basis of the retention test data, it is estimated

JAI

Figure 2. (a)  $V_G$  signals used for programming the memory FET (the one shown in Figure 1) into 4 data states ("00", "01", "10", "11", *i.e.*, a 2-bit memory). (b) Retention characteristics of 4 data states recorded for 3 days. For these retention measurements,  $V_{DS} = 0.01 \text{ V}$ ,  $V_G = 0 \text{ V}$ . It is estimated that these 4 data states can be well discernible within 10 years of the initial applications of programming  $V_G$  signals. (c)  $V_G$  signals for programming another plasma-treated MoS<sub>2</sub> memory FET into 10 data states. (d) Retention characteristics of 10 well-discernible data states recorded for 2000 s. For these 10 retention measurements,  $V_{DS} = 0.05 \text{ V}$ ,  $V_G = 0 \text{ V}$ .

Figure 3. Switching endurance characteristics of a  $MoS_2$  memory FET: (a) Transfer curves ( $I_{DS}-V_G$  curves) corresponding to 8 data states measured for 10 sequential cycles; (b) data levels ( $I_{DS}$  values measured at  $V_{DS} = 0.05$  V,  $V_G = 0$  V after the applications of programming  $V_G$  signals) recorded for 100 sequential cycles (for each endurance characterization cycle, the memory FET is sequentially programmed into "000" to "111" states, demonstrating a repeatable 3-bit memory capability).

that these 10 data levels are distinguishable within day-scale time durations after the initial setting (see Figure S4). Therefore, such a memory FET can enable a 3-bit (at least 8 data levels) storage capability and can be used for electronic applications requiring hour- or day-scale data storage functionalities, such as central processing unit (CPU) cache memories, disposable electronic tags, and buffer memories for displays.

To evaluate the endurance property of multibit memory states, an  $\mathsf{O}_2$  plasma-treated FET was

CHEN ET AL.

periodically programmed into 8 data states (*i.e.*, "0" to "1" to "2" ... to "7", then repeat) by repeatedly applying 8 dual-pulse  $V_{\rm G}$  signals, as indicated in Figure 3a. When the FET was switched into a data state, its current transfer characteristic curve (*i.e.*,  $I_{\rm DS}-V_{\rm G}$  curve for  $V_{\rm G}$  = -10 to 10 V;  $V_{\rm DS}$  = 50 mV) was recorded. Figure 3a shows the transfer curves corresponding to 8 data states that were recorded during the first 10 programming cycles. Figure 3b plots  $I_{\rm DS}$  values (measured under  $V_{\rm G}$  = 0 V,  $V_{\rm DS}$  = 50 mV) of 8 data states recorded

VOL. 8 • NO. 4 • 4023-4032 • 2014

JAI

ARTICLE

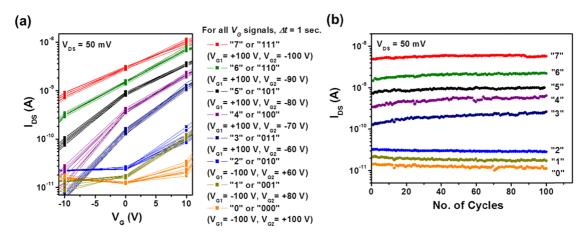

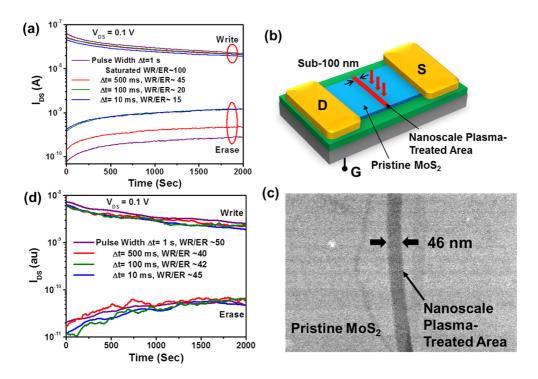

Figure 4. (a) Retention characteristics of the binary data states in a microscale size memory FET (channel length:  $2 \mu$ m, width:  $\sim 5 \mu$ m), which were measured after the device was programmed by  $\pm 100V V_G$  pulses with different pulse durations ( $\Delta t = 10 \text{ ms}$ , 500 ms, and 1 s). (b) Illustration of a MoS<sub>2</sub> memory FET fabricated by using selected-area plasma treatment. Here, the plasma-treated region is a sub-100 nm wide nanoline across the whole MoS<sub>2</sub> channel. (c) SEM image of a 46 nm wide plasma-treated line region across a pristine MoS<sub>2</sub> FET channel that was formed by using O<sub>2</sub> plasma treatment through an EBL-patterned PMMA resist layer. (d) Retention characteristics of the binary data states in the MoS<sub>2</sub> memory FET shown in (c), which were measured after the device was programmed by  $\pm 100V V_G$  pulses with different pulse durations.

for 100 cycles. These results indicate that plasmainduced multibit memory states exhibit a good endurance property.

To evaluate the effect of the  $V_{\rm G}$  pulse duration ( $\Delta t$ ) on the resulting data levels, we measured the retention curves of the binary data levels of an O<sub>2</sub> plasma-treated FET ( $L \approx 2 \ \mu m$ ,  $W \approx 5 \ \mu m$ ) after it was set by applying  $\pm 100$  V V<sub>G</sub> pulses with different time durations ranging from 10 ms to 1 s (Figure 4a). Figure 4a shows that the IDS value of the "write" state exhibits a weak dependence on  $\Delta t$ , whereas the  $I_{\rm DS}$  value of the "erase" state highly depends on  $\Delta t$ , therefore resulting in a strong dependence of the WR/ER ratio on  $\Delta t$ . When  $\Delta t$  is reduced from 1 s to 10 ms, the WR/ER ratio drops from  $\sim$ 100 to 15. This suggests that a long pulse duration  $(\Delta t > 1 \text{ s})$  may be needed to fully charge (or discharge) all plasma-induced charge-trapping states in a microscale size FET. Assuming that the capacitance associated with plasma-induced charge-trapping states is proportional to the total MoS<sub>2</sub> surface area treated with plasma, the required memory setting time is anticipated to be scaled down with reduction of the total plasma-treated area (e.g., using the selected-area plasma treatment). Figure 4b illustrates a MoS<sub>2</sub> memory FET with a selected area treated with plasma. Here, the selected area is a line with a nanoscale width across the whole FET channel. Figure 4c shows a zoomed (in-lens mode) scanning electron microscope (SEM) image of a

CHEN *ET AL*.

MoS<sub>2</sub> FET surface with a 46 nm wide plasma-treated line region across the whole FET channel, which was formed by using O<sub>2</sub> plasma treatment through a PMMA resist layer patterned by electron-beam lithography (EBL). Figure 4d displays the retention curves of binary data levels of this memory FET after it was set by applying  $\pm 100V V_{G}$  pulses with different time durations ranging from 10 ms to 1 s. Although this FET has the same total channel area (*i.e.*,  $L \approx 2 \mu m$ ,  $W \approx 5 \mu m$ ) as that of the blank-treated FET shown in Figure 4a, both its "write" and "erase" IDS values as well as WR/ER ratio exhibit a quite weak dependence on  $\Delta t$  values. This indicates that the selected-area plasma treatment, as compared to the blank treatment, can result in a much smaller capacitance of plasma-induced chargetrapping states and therefore a faster memory setting speed, but can still generate reasonably good WR/ER ratios (40 to 100) suitable for practical memory-related applications. The result shown in Figure 4 also implies that our MoS<sub>2</sub> memory FETs could be scaled down to the smaller devices with sub-50 nm scale channel lengths. Such sub-50 nm size memory FETs are also anticipated to have faster writing/erasing speeds as compared to the current microscale ones.

To explore the physical mechanism responsible for the observed memory capability, we captured SEM images of  $MoS_2$  surfaces treated with  $O_2$  plasma. The SEM image in Figure 5a shows that the  $O_2$  plasma-treated  $MoS_2$

VOL.8 • NO.4 • 4023-4032 • 2014

IAI

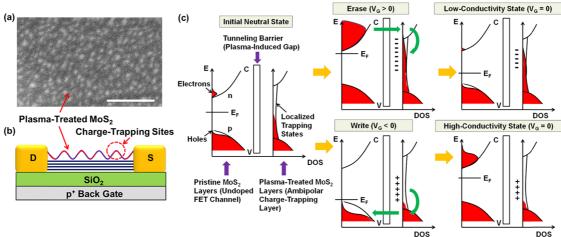

Figure 5. (a) SEM image of an O<sub>2</sub> plasma-treated MoS<sub>2</sub> surface that features nanoscale roughness features (the scale bar is 100 nm). (b) Cross-sectional illustration of a MoS<sub>2</sub> memory FET treated with plasma. The top few MoS<sub>2</sub> layers become rough because of the doping of plasma species. Part of the treated layers may be mechanically separated and electrically insulated from the intact underlying layers and, therefore, can serve as a nonvolatile charge-trapping layer. The plasma-induced gap between this charge-trapping layer and the intact MoS<sub>2</sub> channel can serve as a tunneling barrier layer. (c) Hypothesized write/ erase schemes of plasma-treated MoS<sub>2</sub> memory FETs.

surface exhibits a nanoscale roughness with average period of ~10 nm. Such a roughness, in contrast with the flat surface of a pristine MoS<sub>2</sub> sample, is attributed to the plasma-induced doping of external atoms, which can induce an expansion of the MoS<sub>2</sub> layers and let these layers ripple up and down.<sup>31</sup> This ripple effect could partially exfoliate the plasma-doped top layers from the undoped pristine MoS<sub>2</sub> layers and form charge-trapping sites slightly isolated from the FET channel, as illustrated in Figure 5b. The gap size between such charge-trapping sites and the undoped MoS<sub>2</sub> channel is estimated to be on the same order of magnitude as the average period of the ripple features in the top layers (*i.e.*, 5-10 nm). This gap may serve as a tunneling/blocking barrier layer for retaining trapped charges and switching the memory states. On the basis of this analysis, we have hypothesized a possible write/erase mechanism to preliminarily explain the memory capability of plasma-treated MoS<sub>2</sub> FETs. Figure 5c illustrates the hypothesized band structure (i.e., the density of states (DOS) function) of a plasma-treated MoS<sub>2</sub> FET. The untreated (or pristine) MoS<sub>2</sub> layers (*i.e.*, the FET channel region) are expected to have a typical band structure of lightly doped semiconductors with a relatively low density of impurity states in the band gap, whereas the plasma-treated top layers are expected to exhibit many plasma-induced localized trapping states in the band gap. It is also assumed that these trapping states could be distributed over a broad energy range in the band gap, and they are likely to be a mixture of donor-type, acceptor-type, and isoelectronic deep-level traps. Such a large variety and broad energy distribution of plasma-induced traps are hypothesized based on the fact that energetic plasma species, similar to electron irradiation, could generate a broad variety of defect configurations in MoS<sub>2</sub> layers, including sulfur vacancies, substitutional donor/acceptor

CHEN ET AL.

defects, adatoms with charge, and isoelectronic impurities.<sup>14,31-33</sup> Therefore, the plasma-treated  $MoS_2$  top layers may serve as an ambipolar charge-trapping layer. At the initial neutral state, the net charge in the plasmatreated layers is assumed to be close to zero (i.e., all donor-type traps are occupied with electrons, and all acceptor-type traps are vacant). To obtain an "erase" ("write") state, a positive (negative)  $V_{\rm G}$  pulse is applied. In this case, the Fermi level is elevated (lowered) and the conduction (C) (valence (V)) band of untreated layers (i.e., the FET channel) is populated with electrons (holes). These electrons (holes) have a high probability to tunnel through the barrier and are injected into the conduction (valence) band of the plasma-treated top layers. The injected electrons (holes) may guickly relax to the localized trapping states with lower energies. When the  $V_{G}$  is set back to zero, the trapped electrons (holes) could be retained in the top layers for a long storage time, because of the existence of a barrier layer between plasmatreated and untreated layers as well as the lack of target states in the band gap of untreated layers that can effectively prevent electrons (holes) from tunneling back from the trapping states to the FET channel. This model also implies that the  $V_{\rm G}$  pulse amplitude could modulate the total amount of charged carriers injected into the charge-trapping states in plasma-treated MoS<sub>2</sub> layers. Such trapping states, very likely different from the discrete trap levels in conventional memory FETs with floating gates, may be distributed over a broad energy range and could accommodate different amounts of injected carriers with different polarities, therefore resulting in multiple data levels (i.e., multiple I<sub>DS</sub> values). Such a hypothesized model could preliminarily explain the observed multibit data storage capability. In addition, as implied by this model, the electrons (holes) trapped at relatively high energy states that are close to the

VOL.8 • NO.4 • 4023-4032 • 2014

JAI

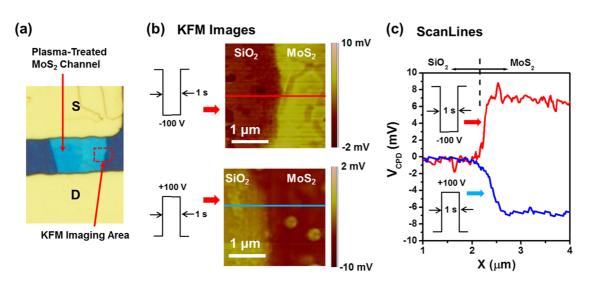

Figure 6. (a) Optical image of a plasma-treated  $MoS_2$  memory FET used for KFM imaging. The dashed box indicates the KFM imaging region. (b) KFM images of the  $MoS_2$  channel captured after the FET was programmed by -100 V, 1 s (top) and +100 V, 1 s (bottom) $V_G$  pulses, respectively. (c) KFM scanlines showing the  $V_{CPD}$  values of the  $MoS_2$  channel after the FET was programmed by -100 V, 1 s (red line) and +100 V, 1 s (blue line)  $V_G$  pulses, respectively.

conduction (valence) band could easily tunnel back to the FET channel and result in a slow relaxation of  $I_{\rm DS}$ values with time. During the initial memory setting, the higher  $V_{\rm G}$  pulse could induce the trapping of more charged carriers in such high-energy states and therefore result in a more prominent relaxation of  $I_{\rm DS}$  values with time. This implication from the model is consistent with our observation in the retention tests (*e.g.*, see Figure 2b and d) that the data states with the highest or the lowest  $I_{\rm DS}$  values, typically configured by  $\pm$  100 V  $V_{\rm G}$  pulses, exhibit more prominent relaxation behaviors than other intermediate data states between them.

To further support our model and verify that plasmatreated MoS<sub>2</sub> layers can indeed serve as chargetrapping layers, we used a Kelvin force microscope (KFM) to image and measure the contact potential (or work function) difference ( $V_{CPD}$ ) between  $V_{G}$ -modulated MoS<sub>2</sub> FET surfaces and the KFM tip. Figure 6a shows the OM of an O<sub>2</sub> plasma-treated MoS<sub>2</sub> FET, in which the dashed box denotes the KFM-imaged area. Figure 6b displays two KFM images that were captured after the FET was configured by applying a -100 V, 1 s  $V_{\text{G}}$  pulse and a +100 V, 1 s V<sub>G</sub> pulse, respectively. The scanlines denoted by the solid lines are accordingly plotted in Figure 6c. Figure 6b and c explicitly show that the polarity switching of the applied  $V_{\rm G}$  pulse can accordingly switch the  $V_{CPD}$  polarity on the MoS<sub>2</sub> surface but does not noticeably change the  $V_{CPD}$  value on the SiO<sub>2</sub> surface. Here, the  $V_{CPD}$  value on the MoS<sub>2</sub> surface is directly associated with the electrostatic interaction between the trapped charge in the top MoS<sub>2</sub> layers and the KFM tip.<sup>34,35</sup> It should be noted that the charge trapped at other interfaces (e.g., MoS<sub>2</sub>/SiO<sub>2</sub> and Si/SiO<sub>2</sub> interfaces) can hardly affect the  $V_{CPD}$  value on the MoS<sub>2</sub> surface because of the screening effect of multilayer MoS<sub>2</sub> channels (the electric-field screening length in

CHEN *ET AL*.

MoS<sub>2</sub> is 3-5 nm; the thickness of our FET channels is 20-30 nm).<sup>35</sup> Therefore, it is concluded that the  $V_{G}$ -modulated memory states observed in our MoS<sub>2</sub> FETs are attributed to the charge-trapping states in plasma-treated top MoS<sub>2</sub> layers, which can enable the ambipolar charge retention and modulation. This conclusion is also consistent with our hypothesized model. Here, although the electric field generated by the back gate is expected not to directly affect the chargetrapping states in the plasma-treated top layers,<sup>35</sup> this gating field can directly modulate the carrier (electron or hole) concentrations in the untreated layers, and these densely populated carriers could diffuse to the interface between untreated and treated layers and subsequently transport through the tunneling barrier formed at this interface, as illustrated in Figure 5c. In this way, the back gate voltage could indirectly modulate the charge trapping and switching in the top MoS<sub>2</sub> layers. Future research will use high-resolution microscopes (e.g., highresolution transmission electron microscopes (HRTEMs)) to directly image the atomic morphology of plasmainduced charge-trapping sites in MoS<sub>2</sub> layers, which is anticipated to provide more precise scientific insights for understanding the observed multibit memory capability.

Finally, we discuss the uniformity issue of our  $MoS_2$  memory FETs. Although it is possible to create reliable individual memory FETs and observe durable multibit memory states in our experiments, our current FETs still exhibit prominent device-to-device variations in WR/ER ratios (*i.e.*, the absolute dynamic range of  $I_{DS}$  values for possible memory states),  $I_{DS}$  values for specific memory states (or data levels), and on/off ratios of initial FETs. Such variations are attributed to our current poor control of the geometry parameters of  $MoS_2$  channels (*i.e.*, width, length, and thickness

VOL. 8 • NO. 4 • 4023-4032 • 2014

IAI

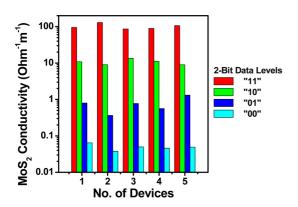

Figure 7. Two-bit data levels (*i.e.*, "00", "01", "10", "11" states) of five  $O_2$  plasma-treated  $MOS_2$  memory FETs fabricated in the same batch. Note that here the data levels are denoted by the conductivity of  $MOS_2$  FET channels instead of  $I_{DS}$  values, which exhibit a reasonably good device-to-device uniformity and consistence.

parameters of MoS<sub>2</sub> FET channels) and the fabricationintroduced unexpected impurities. In particular, different lateral pattern shapes of MoS<sub>2</sub> channels can result in different channel conductance (or IDS) values, different MoS<sub>2</sub> thicknesses can result in different on/off and WR/ER ratios, and unexpected impurities introduced by the fabrication processes could modify the DOS profile of charge-trapping states in plasma-treated MoS<sub>2</sub> layers, resulting in an observable variation in the ratios of  $I_{DS}$  values for multiple data levels. These technical issues need to be addressed to ultimately enable the implementation of our MoS<sub>2</sub> memory FETs into large-area memory cell array architectures. On the basis of current rapid development of 2D-layer technologies, these problems are anticipated to be solved in the near future through developing new nanomanufacturing processes capable of producing highly uniform MoS<sub>2</sub> FET array patterns with well-controlled doping profiles.

To further justify this anticipation, we characterized five memory FETs that were fabricated in the same batch and were expected to have very similar doping profiles in their  $MoS_2$  channels. All five devices have very close  $MoS_2$  channel thicknesses (20 to 25 nm) and lengths (~5  $\mu$ m), but very different channel widths

$(2-10 \ \mu\text{m})$ . To eliminate the effect of lateral pattern shapes on the memory data levels, we used the average conductivity ( $\sigma$ ) values, instead of  $I_{\text{DS}}$  values, of MoS<sub>2</sub> channels to denote the memory states. Figure 7 plots the 2-bit data levels of these five memory FETs, which were measured after the FETs were set by the  $V_{\text{G}}$  signals listed in Figure 2a. Here, these FETs exhibit a reasonably good uniformity and consistency in all plasma-induced data levels. This result implies that through carefully unifying the processing conditions and device geometries, it is highly possible to make large arrays of plasma-treated MoS<sub>2</sub> memory FETs with a high uniformity at all registered data levels.

# CONCLUSION

In conclusion, we dramatically found that the plasma-treated MoS<sub>2</sub> FETs can serve as multibit memory devices with a year-scale 2-bit/transistor (or day-scale 3-bit/transistor) storage capability. SEM and KFM characterization results suggest that such a data storage capability could be attributed to the plasma-induced ripple and partial separation of the top MoS<sub>2</sub> layers from the underlying pristine layers, which could spontaneously form a memory FET structure bearing an ambipolar charge-trapping layer coupled with the FET channel through a tunneling barrier. Such multibit memories exhibit a unique combination of excellent retention and endurance characteristics, extremely simple structures, and low fabrication costs. Our work also shows that the programming speed of such memories can be further improved by using nanoscale-area plasma treatment processes. We anticipate that this work would greatly leverage the unique structural property of MoS<sub>2</sub> and other emerging 2D layered materials for nanoelectronic applications. The presented fabrication methods and device structures hold a significant potential to be further developed into a low cost, upscalable memory solution for making future highperformance disposable electronic products. Especially, our plasma-treated MoS<sub>2</sub> memory FETs with no need of complicated floating-gate structures could be easily scaled down and exhibit a significantly improved writing speed as compared to current MLC memories.

## METHODS AND MATERIALS

Fabrication of the Initial Field-Effect Transistors Using Exfoliated Pristine MoS<sub>2</sub> Flakes. In this work, the initial MoS<sub>2</sub> FETs are fabricated by using a printing-based approach previously published.<sup>15</sup> MoS<sub>2</sub> channel thicknesses ( $t_{MoS2}$ ) are specifically controlled to be 15–30 nm, aiming to achieve relatively high field-effect mobility values ( $\mu = 20$  to 30 cm<sup>2</sup>/Vs).<sup>31,36</sup> The channel lengths (*L*) are 2 to 10  $\mu$ m, and the average channel widths (*W*) are 5 to 15  $\mu$ m. Ti (5 nm)/Au (50 nm) electrode pairs serve as drain (D) and source (S) contacts, which are fabricated by using photolithography followed by metal deposition and lift-off in a solvent. The p<sup>+</sup>-Si substrates are used as back gates (G). Thermally grown SiO<sub>2</sub> layers (300 nm thick) are used as the

CHEN ET AL.

gate dielectrics. Here, the reason that such relatively thick SiO<sub>2</sub> layers are used as gate dielectrics is that we employ a simple color coding method for quickly locating  $MoS_2$  flakes with suitable thicknesses (15–30 nm).<sup>37</sup> In this method,  $MoS_2$  flakes are usually deposited on Si substrates coated with 300 nm thick SiO<sub>2</sub> layers, which can result in an optimal color contrast of few-layer  $MoS_2$  device features against the substrate background under the illumination of a regular photoaligner and can therefore make it convenient to perform overlay alignment. However, using other more advanced tools for imaging  $MoS_2$  features (*e.g.*, a Micro-Raman tool), 300 nm thick gate dielectrics may not be a must here, and our memory FETs could be made on much thinner gate dielectrics to scale down the required programming voltages.

A

Plasma Treatment for Converting MoS<sub>2</sub> FETs into Multibit Memory FETs. The top surface layers of MoS<sub>2</sub> FET channels are treated (or doped) with various plasmas (*i.e.*,  $O_2$ , SF<sub>6</sub>, CF<sub>4</sub>, and CHF<sub>3</sub>) in an inductively coupled plasma-based reactive ion etching tool. For all plasma recipes, the RF power is fixed to 200 W, the pressure is 10 mTorr, the precursor gas flow rate is 10 sccm, and the treatment time for each FET is fixed to 2 min. The surface morphology of plasma-treated MoS<sub>2</sub> FETs is characterized by using a scanning electron microscope.

Electronic Characterizations of Plasma-Induced Binary and Multibit Memory States. The memory FETs are characterized by using a HP4145 semiconductor parameter analyzer that can generate gate voltage ( $V_{\rm G}$ ) pulses with duration widths ranging from 10 ms to 1 s. To characterize the hysteretic behaviors of the transfer curves of memory FETs, drain-source current (I<sub>DS</sub>)-gate voltage (V<sub>G</sub>) curves are acquired along two different V<sub>G</sub> sweep directions with a constant sweep rate of 10 V/s. To configure a memory FET into binary data states, a +100 V (-100 V)  $V_{\rm G}$  pulse (duration  $\Delta t$ : 10 ms to 1 s) is applied to induce a low (high)-conductance "erase" ("write") state in the FET. To evaluate the retention properties of data states, time-dependent I<sub>DS</sub> values (i.e., I<sub>DS</sub>-t curves) are measured under fixed  $V_{DS}$  and  $V_{G}$  (typically  $V_{G} = 0$  and  $V_{DS} =$ 0.01 to 0.1 V) after the initial settings of the memory FET with specific V<sub>G</sub> pulses. A Kelvin force microscope (Veeco NanoMan Dimension V system equipped with Pt/Ir-coated tips with tip radius  $R \approx 20$  nm and resonant frequency  $f_0 \approx 75$  kHz) is employed to probe the polarity and amount of the trapped charge in plasma-treated MoS<sub>2</sub> layers, which are modulated by the V<sub>G</sub> pulse amplitude.

*Conflict of Interest:* The authors declare no competing financial interest.

Supporting Information Available: Transfer curves of an untreated pristine  $MoS_2$  FET (Figure S1); treatment of  $MoS_2$  FETs with water vapor (moisture) by using atomic layer deposition processes; transfer and retention characteristics of a  $MoS_2$  FET treated with moisture (Figure S2); transfer and retention characteristics of FETs treated with CF<sub>4</sub> and CHF<sub>3</sub> plasma recipes (Figure S3); retention characteristics of 10 data states of an O<sub>2</sub> plasma-treated MoS<sub>2</sub> FET (Figure S4). This material is available free of charge via the Internet at http://pubs.acs.org.

Acknowledgment. This work is supported by NSF grant ECCS-1307744. We would like to thank staff of the Univeristy of Michigan's North Campus Electron Microbeam Analysis Laboratory and NSF grants (DMR-0320740 and 0315633) for providing support for SEM imaging. We also thank staff of the University of Michigan's Lurie Nanofabrication Facility for providing support for AFM/KFM imaging and device fabrication and an NSF grant (ECCS-0922972) for providing support for electron-beam lithography.

### **REFERENCES AND NOTES**

- 1. Aritome, S. Advanced Flash Memory Technology and Trends for File Storage Application. *Int. Electron Devices Meet., Tech. Dig.* **2000**, 763–766.

- Katsumata, R.; Kito, M.; Fukuzumi, Y.; Kido, M.; Tanaka, H.; Komori, Y.; Ishiduki, M.; Matsunami, J.; Fujiwara, T.; Nagata, Y.; et al. Pipe-Shaped BiCS Flash Memory with 16 Stacked Layers and Multi-Level-Cell Operation for Ultra High Density Storage Devices. 2009 Symp. VLSI Technol., Digest Tech. Pap. 2009, 136–137.

- Guo, Y. L.; Di, C. A.; Ye, S. H.; Sun, X. N.; Zheng, J.; Wen, Y. G.; Wu, W. P.; Yu, G.; Liu, Y. Q. Multibit Storage of Organic Thin-Film Field-Effect Transistors. *Adv. Mater.* 2009, *21*, 1954– 1959.

- Sohn, J. I.; Choi, S. S.; Morris, S. M.; Bendall, J. S.; Coles, H. J.; Hong, W. K.; Jo, G.; Lee, T.; Welland, M. E. Novel Nonvolatile Memory with Multibit Storage Based on a ZnO Nanowire Transistor. *Nano Lett.* **2010**, *10*, 4316–4320.

- Lee, J. S.; Kim, Y. M.; Kwon, J. H.; Sim, J. S.; Shin, H.; Sohn, B. H.; Jia, Q. X. Multilevel Data Storage Memory Devices Based on The Controlled Capacitive Coupling of Trapped Electrons. *Adv. Mater.* 2011, *23*, 2064–2068.

- Nirschl, T.; Philipp, J. B.; Flapp, T. D.; Burr, G. W.; Rajendran, B.; Leeo, M. H.; Schrott, A.; Yang, M.; Breitwisch, M.; Chen, C. F.; et al. Write Strategies for 2 and 4-Bit Multi-Level Phase-Change Memory. 2007 IEEE Int. Electron Devices Meet. 2007, 1 and 2, 461–464.

- Kwak, D.; Park, J.; Kim, K.; Yim, Y.; Ahn, S.; Park, Y.; Kim, J.; Jeong, W.; Kim, J.; Park, M.; *et al.* Integration Technology of 30 nm Generation Multi-Level NAND Flash for 64 Gb NAND Flash Memory. *2007 Symp. VLSI Technol., Digest Techn. Pap.* **2007**, 12–13.

- Zhou, Y.; Han, S. T.; Sonar, P.; Roy, V. A. L. Nonvolatile Multilevel Data Storage Memory Device from Controlled Ambipolar Charge Trapping Mechanism. *Sci. Rep.* 2013, *3*, 2319/1–2319/7.

- Pellegrino, L.; Manca, N.; Kanki, T.; Tanaka, H.; Biasotti, M.; Bellingeri, E.; Siri, A. S.; Marre, D. Multistate Memory Devices Based on Free-standing VO<sub>2</sub>/TiO<sub>2</sub> Microstructures Driven by Joule Self-Heating. *Adv. Mater.* **2012**, *24*, 2929– 2934.

- Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-Layer MoS<sub>2</sub> Transistors. *Nat. Nanotechnol.* **2011**, 6, 147–150.

- Pu, J.; Yomogida, Y.; Liu, K. K.; Li, L. J.; Iwasa, Y.; Takenobu, T. Highly Flexible MoS<sub>2</sub> Thin-Film Transistors with Ion Gel Dielectrics. *Nano Lett.* **2012**, *12*, 4013–4017.

- Korn, T.; Heydrich, S.; Hirmer, M.; Schmutzler, J.; Schuller, C. Low-Temperature Photocarrier Dynamics in Monolayer MoS<sub>2</sub>. Appl. Phys. Lett. **2011**, *99*, 102109/1–102109/3.

- Mak, K. F.; Lee, C.; Hone, J.; Shan, J.; Heinz, T. F. Atomically Thin MoS<sub>2</sub>: A New Direct-Gap Semiconductor. *Phys. Rev. Lett.* **2010**, *105*, 136805/1–136805/4.

- Chhowalla, M.; Shin, H. S.; Eda, G.; Li, L. J.; Loh, K. P.; Zhang, H. The Chemistry of Two-Dimensional Layered Transition Metal Dichalcogenide Nanosheets. *Nat. Chem.* **2013**, *5*, 263–275.

- Nam, H.; Wi, S.; Rokni, H.; Chen, M.; Priessnitz, G.; Lu, W.; Liang, X. MoS<sub>2</sub> Transistors Fabricated via Plasma-Assisted Nanoprinting of Few-Layer-MoS<sub>2</sub> Flakes into Large-Area Arrays. ACS Nano 2013, 7, 5870–5881.

- Wang, H.; Yu, L. L.; Lee, Y. H.; Shi, Y. M.; Hsu, A.; Chin, M. L.; Li, L. J.; Dubey, M.; Kong, J.; Palacios, T. Integrated Circuits Based on Bilayer MoS<sub>2</sub> Transistors. *Nano Lett.* **2012**, *12*, 4674–4680.

- Zhang, Y. J.; Ye, J. T.; Matsuhashi, Y.; Iwasa, Y. Ambipolar MoS<sub>2</sub> Thin Flake Transistors. *Nano Lett.* **2012**, *12*, 1136–1140.

- Chen, J. R.; Odenthal, P. M.; Swartz, A. G.; Floyd, G. C.; Wen, H.; Luo, K. Y.; Kawakami, R. K. Control of Schottky Barriers in Single Layer MoS<sub>2</sub> Transistors with Ferromagnetic Contacts. *Nano Lett.* **2013**, *13*, 3106–3110.

- Das, S.; Chen, H. Y.; Penumatcha, A. V.; Appenzeller, J. High Performance Multilayer MoS<sub>2</sub> Transistors with Scandium Contacts. *Nano Lett.* **2013**, *13*, 100–105.

- Salvatore, G. A.; Munzenrieder, N.; Barraud, C.; Petti, L.; Zysset, C.; Buthe, L.; Ensslin, K.; Troster, G. Fabrication and Transfer of Flexible Few-Layers MoS<sub>2</sub> Thin Film Transistors to Any Arbitrary Substrate. ACS Nano **2013**, 7, 8809–8815.

- Chang, H. Y.; Yang, S. X.; Lee, J. H.; Tao, L.; Hwang, W. S.; Jena, D.; Lu, N. S.; Akinwande, D. High-Performance, Highly Bendable MoS<sub>2</sub> Transistors with High-*k* Dielectrics for Flexible Low-Power Systems. ACS Nano **2013**, 7, 5446– 5452.

- Lembke, D.; Kis, A. Breakdown of High-Performance Mono layer MoS<sub>2</sub> Transistors. ACS Nano 2013, 7, 3730–3730.

- Late, D. J.; Huang, Y. K.; Liu, B.; Acharya, J.; Shirodkar, S. N.; Luo, J. J.; Yan, A. M.; Charles, D.; Waghmare, U. V.; Dravid, V. P.; *et al.* Sensing Behavior of Atomically Thin-Layered MoS<sub>2</sub> Transistors. *ACS Nano* **2013**, *7*, 4879–4891.

- Perera, M. M.; Lin, M. W.; Chuang, H. J.; Chamlagain, B. P.; Wang, C. Y.; Tan, X. B.; Cheng, M. M. C.; Tomanek, D.; Zhou, Z. X. Improved Carrier Mobility in Few-Layer MoS<sub>2</sub> Field-Effect Transistors with Ionic-Liquid Gating. ACS Nano 2013, 7, 4449–4458.

- Bertolazzi, S.; Krasnozhon, D.; Kis, A. Nonvolatile Memory Cells Based on MoS<sub>2</sub>/Graphene Heterostructures. ACS Nano 2013, 7, 3246–3252.

- Choi, M. S.; Lee, G. H.; Yu, Y. J.; Lee, D. Y.; Lee, S. H.; Kim, P.; Hone, J.; Yoo, W. J. Controlled Charge Trapping by Molybdenum Disulphide and Graphene in Ultrathin Heterostructured Memory Devices. *Nat. Commun.* **2013**, *4*.

- Lee, H. S.; Min, S. W.; Park, M. K.; Lee, Y. T.; Jeon, P. J.; Kim, J. H.; Ryu, S.; Im, S. MoS<sub>2</sub> Nanosheets for Top-Gate Nonvolatile Memory Transistor Channel. *Small* **2012**, *8*, 3111–3115.

- Yin, Z. Y.; Zeng, Z. Y.; Liu, J. Q.; He, Q. Y.; Chen, P.; Zhang, H. Memory Devices Using a Mixture of MoS<sub>2</sub> and Graphene Oxide as the Active Layer. *Small* **2013**, *9*, 727–731.

- Liu, J. Q.; Zeng, Z. Y.; Cao, X. H.; Lu, G.; Wang, L. H.; Fan, Q. L.; Huang, W.; Zhang, H. Preparation of MoS<sub>2</sub>-Polyvinylpyrrolidone Nanocomposites for Flexible Nonvolatile Rewritable Memory Devices with Reduced Graphene Oxide Electrodes. *Small* **2012**, *8*, 3517–3522.

- Late, D. J.; Liu, B.; Matte, H. S. S. R.; Dravid, V. P.; Rao, C. N. R. Hysteresis in Single-Layer MoS<sub>2</sub> Field Effect Transistors. ACS Nano 2012, 6, 5635–5641.

- Chen, M.; Nam, H.; Wi, S.; Lian, J.; Ren, X.; Bian, L. F.; Lu, S.; Liang, X. G. Stable Few-Layer MoS<sub>2</sub> Diodes Formed by Plasma-Assisted Doping. *Appl. Phys. Lett.* **2013**, *103*, 142110/1–142110/4.

- Yue, Q.; Chang, S. L.; Qin, S. Q.; Li, J. B. Functionalization of Monolayer MoS<sub>2</sub> by Substitutional Doping: A First-Principles Study. *Phys. Lett. A* **2013**, *377*, 1362–1367.

- Komsa, H. P.; Kotakoski, J.; Kurasch, S.; Lehtinen, O.; Kaiser, U.; Krasheninnikov, A. V. Two-Dimensional Transition Metal Dichalcogenides under Electron Irradiation: Defect Production and Doping. *Phys. Rev. Lett.* **2012**, *109*, 035503/ 1–035503/5.

- Nonnenmacher, M.; Oboyle, M. P.; Wickramasinghe, H. K. Kelvin Probe Force Microscopy. *Appl. Phys. Lett.* **1991**, *58*, 2921–2923.

- Li, Y.; Xu, C. Y.; Zhen, L. Surface Potential and Interlayer Screening Effects of Few-Layer MoS<sub>2</sub> Nanoflakes. *Appl. Phys. Lett.* **2013**, *102*, 143110/1–143110/4.

- Bao, W. Z.; Cai, X. H.; Kim, D.; Sridhara, K.; Fuhrer, M. S. High Mobility Ambipolar MoS<sub>2</sub> Field-Effect Transistors: Substrate and Dielectric Effects. *Appl. Phys. Lett.* **2013**, *102*, 042104/1–042104/3.

- Zhang, Y. J.; Ye, J. T.; Yomogida, Y.; Takenobu, T.; Iwasa, Y. Formation of a Stable p-n Junction in a Liquid-Gated MoS<sub>2</sub> Ambipolar Transistor. *Nano Lett.* **2013**, *13*, 3023– 3028.